台积电(TSM.US)黄汉森:2050年晶体管能做到0.1纳米,氢原子尺度!

本文来自微信公众号“ittbank”。文中观点不代表智通财经观点。

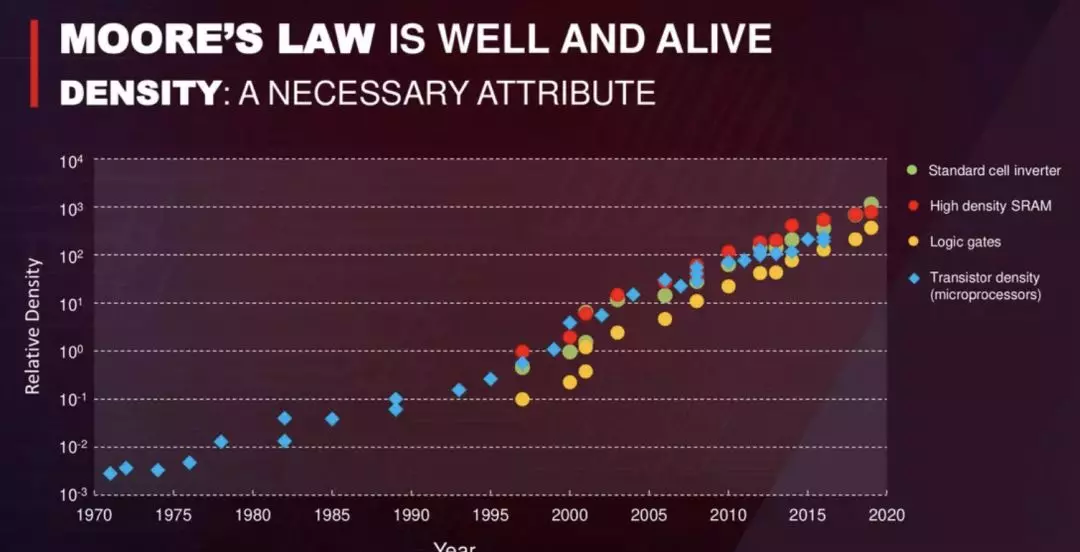

台积电(TSM.US)研发负责人Phillip Wong近日在硅谷举行的Hot Chips会议上表示,摩尔定律没死,依然有效且状况良好,并表示随着新技术的进步,到2050年晶体管做到0.1纳米,约等于氢原子的大小。

“毋庸置疑,摩尔定律依然有效且状况良好,它没有死掉,没有减速,也没有生病。”

台积电研发负责人Philip Wong(黄汉森)在Hot chips大会上表示,他展示了台积电对芯片技术的前瞻,称到2050年,晶体管将缩小到氢原子尺度,即0.1nm。

黄汉森去年8月开始担任台积电企业研究副总裁,在此之前他是斯坦福大学电机工程学系教授,擅长新形态的存储技术研究,在学术界拥有很高声望。

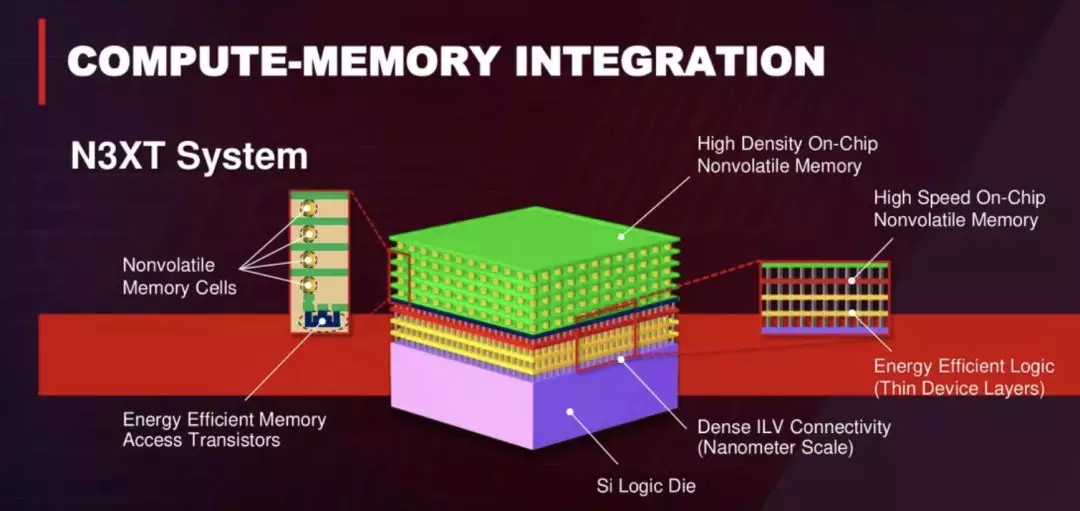

黄汉森在Hot Chips大会上演讲的题目是:“下一个半导体工艺节点会给我们带来什么?” ,他还详细介绍了其他芯片技术的发展,比如将内存放在处理器的正上方,他预计这将提高性能。

对摩尔定律非常乐观,台积电提出芯片进展的三大方向

摩尔定律预测,集成电路上可容纳的晶体管数量,约每隔 18 个月便会增加一倍,性能也将提升一倍(即更多的晶体管使其更快)。

不过,如何以最有经济效益的方法将数十亿个晶体管放在一颗芯片中,成为当前芯片制造遇到的最大挑战,所以近年来有不少人认为摩尔定律逼近了物理极限并开始放缓。

英特尔一直在努力研发先进制程,但从整个行业来看,单个晶体管的价格不再继续下降。这就限制了新的制造工艺只能用于高端、高成本的芯片。过去芯片行业的好日子已经一去不复返了,那时芯片的时钟速度提高,功耗却没有受到任何影响。

因此,芯片制造业出现悲观主义者也就不足为奇。

黄汉森预计,处理器将由不同芯片元件3D堆叠组成,而在当前这些元件通常是分开的。这将意味着芯片获得更小的尺寸和更高的性能。

不过,作为晶圆代工龙头的台积电却非常乐观。黄汉森表示,摩尔定律进展良好,并大胆地预测了到2050年的进展,尽管他没有提供任何详细的计划。

摩尔定律以及芯片进展的其他方面都状况良好

Real World Technologies的分析师David Kanter则更为谨慎。由于台积电现在与英特尔已经是并列,而不是在英特尔之后,台积电不得不承担更多的领导责任,加大研发投入,因此听到该公司如此乐观并不令人意外。但谈到芯片的进步,黄汉森对一些实际问题避而不谈,比如缩小晶体管的速度放缓,以及制造最新一代产品的成本增加。

根本性的改进

“我们期待看到更多不同方向的创新,这将为行业提供持续的利益。”黄汉森说:“这就是我们关心的。”

黄汉森表示,芯片技术的元件正在缩小到极小的尺寸

关于未来的技术路线,Philip Wong 认为像碳纳米管(1.2nm 尺度),2D层状材料等可以将晶体管变得更快,尺寸更小;同时,相变内存(PRAM),旋转力矩转移随机存取内存(STT-RAM)等会直接和处理器封装在一起,缩小体积,加快数据传递速度;此外还有 3D 堆叠封装技术。

具体而言,黄汉森就未来的发展方向提出若干观点:

新技术将使晶体管更快、更小。长期以来一直在考虑的一项技术——碳纳米管,现在正变得切实可行。另一种是被称为2D层状材料的材料,可以通过让电子更容易地流过芯片来提供类似的增强。

一些新的内存技术将直接构建到处理器中,而不是作为单独的芯片连接。这种快速连接将极大地提高性能,因为芯片上的逻辑电路(处理数据的部分)将更快地获得所需的数据,因此不必有太多闲置时间。

3D堆叠技术将意味着,如今孤立的计算机处理器功能可以被夹在多个层中,与高速数据通路相连。

“在这些系统中,多层逻辑和内存以细粒度的方式集成,连接性是关键,”黄汉森说。

分析师Nathan Brookwood表示,尽管黄汉森对碳纳米管等技术非常关注,但不认为台积电本身在现阶段会押注于任何特定的新技术。

新的计算机内存技术将取得进展

不过,黄汉森强调,除了硬件,软件算法也需要迎头赶上。一旦实现了这一点,芯片的进步将提供更好的计算设备。这是至关重要的,黄汉森说:“社会对先进技术的需求是无止境的。”

台积电Hot Chips大会演讲精编

摩尔定律讲的是元件密度,这是高性能计算的主要驱动力。

从对数图上看,摩尔定律不但没有死,而且活的很好,晶体管密度还在增加,而且在可预见的未来内还会继续增加,至于时钟速度和运行效率等人们同样关心的新属性,实际上超出了摩尔定律的范围。

进入AI和5G时代,“内存墙”问题日益突出,海量数据的流动和转移的需求越来越高,内存访问决定了计算的能源效率。

深度神经网络需要大量的内存容量,而且内存紧缺的问题将来还会更加突出。芯片上需要更多数量的SRAM,但永远都不够,重要的是什么样的内存。

现有的系统中,大部分都是2D和2.5D,用的是TSV,我们需要再向前迈进一步,进入3D。

而下一步就是Beyond 3D,它实现了逻辑和内存的多层整合,在纳米级尺度上实现了高密度的TSV工艺,即“N3XT级”系统。

下一代内存需要具备高带宽、高容量,而且需要在片上。

研究表明,具备上述条件的内存可以使系统级收益增加近2000倍,当然,以现有技术很难实现。在上层很难构建高性能晶体管,因为制造时需要1000度高温条件,内存层会融化。

要想实现上面说的理想的系统,需要超薄的设备层和较低的制造温度。

近年来,晶体管技术实现了不少进步,出现了2D层材料过度金属设计,1D碳纳米管设计等,这些材料非常轻薄,大大降低了晶体管的沟道宽度,但仍保持高迁移率水平。

实现内存与逻辑平台在3D架构下的整合,让晶体管与制造技术的进步成为一个连续的统一体。

而要实现这一目标,各自为战是不行的。这需要系统工程师和开发人员的密切合作,需要硬件设备制造技术和需求的更紧密的交流,需要学术界与产业界建立更加紧密的联系。

扫码下载智通APP

扫码下载智通APP